DATA TRANSFER INSTRUCTION

instructions, which are used to transfer data from one register to another register, from memory to register or register to memory are Data Transfer Instruction. when data transfer instructions is executed, data is transferred from the source to the destination without altering the contents of the source.

| Opcode | Operand | Description |

|---|---|---|

| MOV | Rd,Rs M,Rs Rd,M |

Copy from source to destination |

| MVI | Rd,Data M,Data |

Move immediate 8-bit |

| LDA | 16-bit address | Load Accumulator |

| LDAX | B/D Register Pair | Load accumulator indirect |

| LXI | Register pair, 16-bit data | Load register pair immediate |

| LHLD | 16-bit address | Load H-L registers direct |

| STA | 16-bit address | Store accumulator direct |

| STAX | Register pair | Store accumulator indirect |

| SHLD | 16-bit address | Store H-L registers direct |

| XCHG | None | Exchange H-L with D-E |

| SPHL | None | Copy H-L pair to the Stack Pointer (SP) |

| XTHL | None | Exchange H–L with top of stack |

| PCHL | None | Load program counter with H-L contents |

| PUSH | Register pair | Push register pair onto stack |

| POP | Register pair | Pop stack to register pair |

| OUT | 8-bit port address | Copy data from accumulator to a port with 8- bit address |

| IN | 8-bit port address | Copy data to accumulator from a port with 8- bit address |

1) MOV instruction:

This instruction copies the contents of the source register into the destination register. The contents of the source register are not altered.If one of the operands is a memory location, its location is specified by the contents of the HL registers.These instructions are of one byte instruction and no flag is affected in these instructions.

(i) MOV reg1, reg2 (Moves to register from register)

where reg = A, B, C, D, E, H or L

This instruction is moves / copies the data in the given register to the given register.

i.e

[reg1] < - [reg2]

(ii) MOV reg, M (Moves to register from memory)

This instruction is indirect read instruction. It moves / copies the data stored in

memory location whose address is given in H-L register pair, to the given register.

i.e

[reg] < - [MHL]

(iii) MOV M, reg (Moves to memory from register)

This instruction moves / copies the data in the given register to the memory

location addressed by H-L register pair.

i.e

[MHL] < - [reg]

For example let D = 4E H, H = 23 H, L = 00 H Then after execution of the instruction MOV M, D will produce the result:

[M2300] < - [4E]

| Operand | Bytes | Flags Affected | M-Cycles | T-States |

|---|---|---|---|---|

| Rd,Rs | 1 | None | 1 | 4 |

| Rd,M | 1 | None | 2 | 7 |

| M,Rs | 1 | None | 2 | 7 |

2) MVI instruction:

This an instruction to load register with 8-bit value. This instruction uses immediate addressing for specifying the data.If the operand is a memory location, its location is specified by the contents of the H-L registers.These instructions are two byte instructions and no flag is affected.

(i) MVI reg, 8 bit data (Moves 8 bit data to register)

This instruction transfers the given data to the register.

i.e

[reg] < - [8 bit data]

(ii) MVI M, 8 bit data (Moves 8 bit data to memory)

This instruction transfers the given data to the memory location pointed by H-L pair.

i.e

[MHL] < - [8 bit data]

For example the given data 2BH will be copied into the memory location whose address is given in H-L register pair. If H = 21 H, L = 00 H then,

MVI M,2B

[M2100] < - [2B]

| Operand | Bytes | Flags Affected | M-Cycles | T-States |

|---|---|---|---|---|

| Rd,data | 2 | None | 2 | 7 |

| M,data | 2 | None | 3 | 10 |

3) LDA instruction:

This is mnemonic for Loads the accumulator direct. It transfers the content stored in the addressed memory location (given by address) to accumulator. No flag is affected in this instruction. It is three byte instruction.

[A] < - [Maddress]

For example if 2A H data is stored in memory location 2500H before the execution of

LDA 2500H

instruction, then after the execution of this instruction, the data 2AH will be transferred to accumulator.

[A] < - [2A]

| Operand | Bytes | Flags Affected | M-Cycles | T-States |

|---|---|---|---|---|

| 16-bit address | 3 | None | 4 | 13 |

4) LDAX instruction:

This is mnemonic for Loads the Accumulator Indirect. the contents already stored in the memory location addressed by the register pair (rp). Here rp represents B-C or D-E register pair.

The H-L register pair is not included in this instruction.the instruction LDAX H does not exist, because the contents stored in the memory location addressed by H-L register pair may be loaded to accumulator by the instruction MOV A, M.The possible combinations of the instruction are:

LDAX B

LDAX D

For example, if [D] = 25 H, [E] = 00 H and M2500 H = 34 H, then after the execution of the instruction LDAX D, the accumulator will have:

[A] < - [M2500] , A = 34 H

| Operand | Bytes | Flags Affected | M-Cycles | T-States |

|---|---|---|---|---|

| B/D Register Pair | 1 | None | 2 | 7 |

5) LXI instruction:

This is mnemonic for Load eXtended register Immediate. Here, a register pair is termed as extended register. It is an instruction that loads register pair 'rp' with the 16-bit data. This instruction uses immediate addressing for specifying the data.

where rp = BC,DE,HL

i.e LXI rp,16 bit data

For example if you want to load HL with F850 H then,

LXI H,F850H

| Operand | Bytes | Flags Affected | M-Cycles | T-States |

|---|---|---|---|---|

| Reg. pair,16-bit data | 3 | None | 3 | 10 |

6) LHLD instruction:

This is mnemonic for Loads the H-L pair direct.This instruction loads the H-L pair direct with two bytes already stored in two consecutive memory locations starting at the specified memory address. The contents stored in the memory location whose address is given with the instruction will be loaded to the L-register; and the contents stored in the next memory location (address + 1) will be loaded to the H-register.

LHLD 2100 H

after the execution of the instruction LHLD 2100 H , the L-register will have 2A H and H-register will have 2B H.

| Operand | Bytes | Flags Affected | M-Cycles | T-States |

|---|---|---|---|---|

| 16-bit address | 3 | None | 5 | 16 |

7) STA instruction:

This is mnemonic for Stores the accumulator direct.It transfers the content stored in the accumulator to addressed memory location (given by address).

16H data is stored in the accumulator before the execution of STA 2100H instruction

STA 2100 H

after the execution of this instruction, the data 16H will be transferred to the addressed memory location.

[Maddress] < - [A]

| Operand | Bytes | Flags Affected | M-Cycles | T-States |

|---|---|---|---|---|

| 16-bit address | 3 | None | 4 | 13 |

8) STAX instruction:

This is mnemonic for Stores the Accumulator Indirect.The STAX rp instruction does the reverse operation of LDAX rp. This instruction stores the accumulator contents in the memory location addressed by the register pair (rp). Here too rp represents B-C or D-E register pair.

The combination STAX H is not included in this instruction as MOV A, M performs the same operation.The possible combination of this instruction are:

STAX B

STAX D

For example, if B = 21 H, C = 00 H and A = 3A H,

STAX B

after the execution of the instruction STAX B, 3A H will be stored in the memory location 2100 H.

[Mrp] < - [A]

| Operand | Bytes | Flags Affected | M-Cycles | T-States |

|---|---|---|---|---|

| B/D Register Pair | 1 | None | 2 | 7 |

9) SHLD instruction:

This is mnemonic for Stores the H-L pair direct.This instruction does the reverse operation of LHLD. The instruction SHLD address stores the contents of L-register to memory location whose address is given with the instruction; and the contents of H-register are stored in the next consecutive memory location (address + 1).

For example, if [L]= 3A H and[H] = 3B H,

SHLD 2200 H

after the execution of the instruction SHLD 2200 H will result.

[M2200H] < - 3A

[M2201H] < - 3B

| Operand | Bytes | Flags Affected | M-Cycles | T-States |

|---|---|---|---|---|

| 16-bit address | 3 | None | 5 | 16 |

10) XCHG instruction:

This is mnemonic for Exchange the contents of H-L register with D-E register.This is one byte instruction and no operand is needed with it. It exchanges the contents of H and L register with D and E registers respectively.

For example:If H = 25 H , L = 32 H and D = 12 H, E = 1B H,

XCHG

after the execution of XCHG instruction, we have:H = 12 H, L = 1B H and D = 25 H, E = 32 H.

[H] < - > [D] and [L] < - > [E]

| Operand | Bytes | Flags Affected | M-Cycles | T-States |

|---|---|---|---|---|

| None | 1 | None | 1 | 4 |

11) SPHL instruction:

This is mnemonic for Copies HL to Stack Pointer SP.This is also one byte instruction as no operand is used. The SPHL instruction copies the contents of H-register to high order byte stack pointer (SP) and the contents of L-register to low order byte of stack pointer (SP).

For example if H = 23 H and L = 45 H and SP = 2501 H,

SPHL

after the execution of the instruction SPHL will result SP = 2345 H.

[SP] < - > [HL] i.e. [SPH] < - > [H] and [SPL] < - > [L]

| Operand | Bytes | Flags Affected | M-Cycles | T-States |

|---|---|---|---|---|

| None | 1 | None | 1 | 6 |

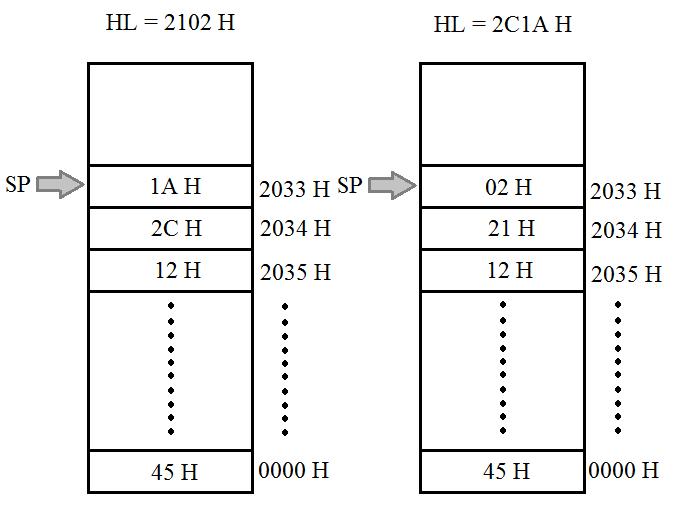

12) XTHL instruction:

This is mnemonic for Exchanges the top of the stack with H-L register pair.The XTHL is one byte instruction and does not require any operand. The top byte of the stack is exchanged with L-register and next byte of the stack is exchanged with H-register.

| Operand | Bytes | Flags Affected | M-Cycles | T-States |

|---|---|---|---|---|

| None | 1 | None | 5 | 16 |

For example if H = 21 H, L = 02 H and MSP =1A H, MSP+1 = 2C H,

XTHL

then after the execution of the instruction XTHL will result:

H = 2C H, L = 1A H and MSP = 02 H, MSP+1 = 21 H

as shown in figure

13) PCHL instruction:

This is mnemonic for Copies H-L to program counter (PC).This is one byte instruction and no operand is needed with this instruction. It copies the contents of H-register to high-order byte of the program counter (PC) and the contents of L-register to low order byte of the program counter.

For example if PC = 2106 H and HL = 2500 H,

PCHL

after the execution of the instruction PCHL will result: PC = 2500 H.

[PC] < - > [HL] i.e. [PCH] < - > [H] and [PCL] < - > [L]

| Operand | Bytes | Flags Affected | M-Cycles | T-States |

|---|---|---|---|---|

| None | 1 | None | 1 | 6 |

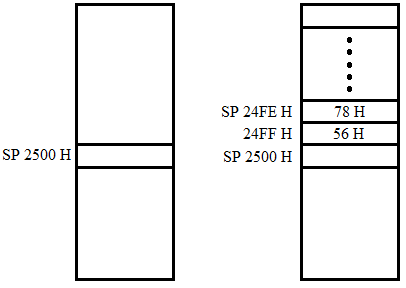

14) PUSH instruction:

This instruction use to push the contents of registers to the stack. In the stack not only the return address of the main program during the execution of CALL address instruction is pushed but also the contents of registers may also be pushed to stack.

where rp = BC,DE,HL,PSW

PUSH rp

| Operand | Bytes | Flags Affected | M-Cycles | T-States |

|---|---|---|---|---|

| Register pair | 1 | None | 3 | 12 |

For example we have SP = 2500 H, HL = 5678 H,

PUSH H

After the execution of PUSH H instruction 56 H will be loaded to memory location 24FF H and 78 H will be loaded to 24FE H memory location.

as shown in figure

PSW :Here AF is register pair formed with Flag and Accumulator register and also known as PSW(Processor Status Word).In PSW, Accumulator is the MS Byte, and Flags register is the LS Byte.

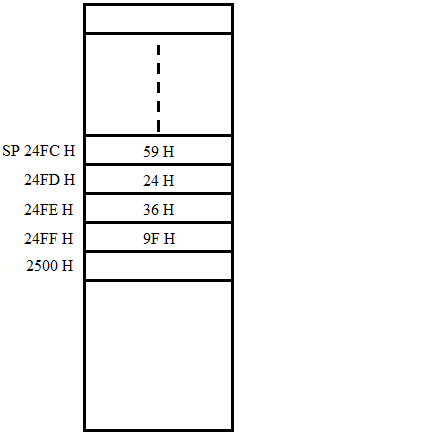

15) POP instruction:

This instruction use To retrieve the contents of registers from the stack.

where rp = BC,DE,HL,PSW

POP rp

| Operand | Bytes | Flags Affected | M-Cycles | T-States |

|---|---|---|---|---|

| Register pair | 1 | None | 3 | 10 |

For example the data saved in stack is shown in figure and A = 01 H, F = 00 H,D = 12 H, E = 6E H,

POP PSW

POP D

After the execution of these instructions we have the following data in the registers.F = 59 H, A = 24 H, E = 36 H, D = 9F H. Now 2500 H will be the new value of stack pointer.

16) OUT instruction:

This is mnemonic for Outputs the data to the port.This two byte output instruction is used to send the contents of accumulator to the specified port.

OUT port

Output < - [A]

| Operand | Bytes | Flags Affected | M-Cycles | T-States |

|---|---|---|---|---|

| 8-bit port address | 2 | None | 3 | 10 |

17) IN instruction:

This is mnemonic for Inputs the data from the port.This instruction is basically used to read the data from the input devices such as data read from key board, switches etc. during the computer run.

IN port

[A] < - data from port

| Operand | Bytes | Flags Affected | M-Cycles | T-States |

|---|---|---|---|---|

| 8-bit port address | 2 | None | 3 | 10 |